#### 8-BIT 3CH fC BUS D-A CONVERTER WITH BUFFER AMPLIFIERS

#### **DESCRIPTION**

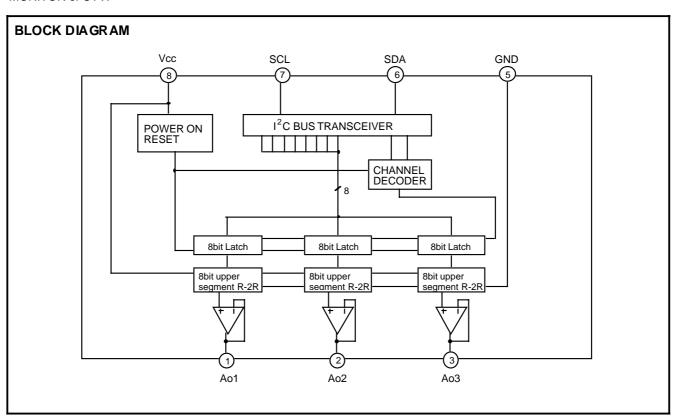

The M62333/M62338 is an integrated circuit semiconductor of CMOS structure with 3 channels of built in D-A converters with output buffer operational amplifiers.

The input is 2-wires serial method is used for the transfer format of digital data to allow connection with a microcomputer with minimum wiring.

The output buffer operational amplifier employs AB class output circuit with sync and source drive capacity of 1.0mA or more,and it operates in the whole voltage range from Vcc to ground.

The M62333 and the M62338 differ only in their slave address.

#### **FEATURES**

- Digital data transfer format I<sup>2</sup>C BUS serial data method

- Output buffer operational amplifier it operates in the whole voltage range from Vcc to

- ground.High output current drive capacity ±1.0mA over

#### **APPLICATION**

Conversion from digital data to analog control data for home-use and industrial equipment.

Signal gain control or automatic adjustment of DISPLAY-MONITOR or CTV.

## 8-BIT 3CH FC BUS D-A CONVERTER WITH BUFFER AMPLIFIERS

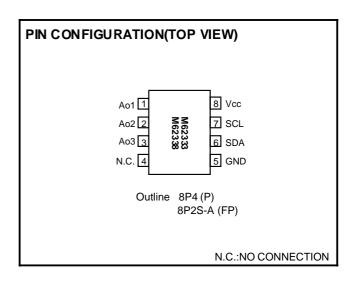

#### **EXPLANATION OF TERMINALS**

| Pin No. | Symbol | Function                                       |  |  |  |  |  |  |  |

|---------|--------|------------------------------------------------|--|--|--|--|--|--|--|

| 6       | SDA    | Serial data input terminal                     |  |  |  |  |  |  |  |

| 7       | SCL    | erial clock input terminal                     |  |  |  |  |  |  |  |

| 1       | Ao1    |                                                |  |  |  |  |  |  |  |

| 2       | Ao2    | 3-bit resolution D-A converter output terminal |  |  |  |  |  |  |  |

| 3       | Ao3    |                                                |  |  |  |  |  |  |  |

| 8       | Vcc    | Power supply terminal                          |  |  |  |  |  |  |  |

| 5       | GND    | GND terminal                                   |  |  |  |  |  |  |  |

### **ABSOLUTE MAXIMUM RATING**

| Symbol | Parameter             | Parameter Conditions |                      | Unit |

|--------|-----------------------|----------------------|----------------------|------|

| Vcc    | Supply voltage        |                      | -0.3 to 7.0          | V    |

| Vin    | Input voltage         |                      | -0.3 to Vcc+0.3      | V    |

| Vo     | Output voltage        |                      | -0.3 to Vcc+0.3      | V    |

| Pd     | Power dissipation     |                      | 417 (DIP) / 272 (FP) | mW   |

| Topr   | Operating temperature |                      | -20 to 85            | °C   |

| Tstg   | Storage temperature   |                      | -55 to 125           | °C   |

## **ELECTRICAL CHARACTERISTICS** (Vcc=+5V±10%,GND=0V,Ta=-20 to 85°C unless otherwise noted)

|        |                                     |                                                                          |        | 1.1 |         |      |

|--------|-------------------------------------|--------------------------------------------------------------------------|--------|-----|---------|------|

| Symbol | Parameter                           | Test conditions                                                          | MIN    | TYP | MAX     | Unit |

| Vcc    | Suplly voltage                      |                                                                          | 2.7    | 5.0 | 5.5     | ٧    |

| lcc    | Supply current                      | CLK=500kHz Operation, IAO=0µA<br>Data : 6Ah (at maximum current )        | 0      | 0.9 | 2.7     | mA   |

| 100    | Оприу синсти                        | SDA=SCL=GND,IAO=0µA                                                      | 0      | 0.6 | 1.8     | mA   |

| lilk   | Input leak current                  | VIN=0 to Vcc                                                             | -10    |     | 10      | μΑ   |

| VIL    | Input low voltage                   |                                                                          |        |     | 0.2Vcc  | V    |

| VIH    | Input high voltage                  |                                                                          | 0.8Vcc |     |         | ٧    |

| VAO    | Buffer amplifier output             | IAO=±100μA                                                               | 0.1    |     | Vcc-0.1 | V    |

| VAO    | voltage range                       | IAO=±500μA                                                               | 0.2    |     | Vcc-0.2 | V    |

| IAO    | Buffer amplifier output drive range | Upper side saturation voltage=0.3V<br>Lower side saturation voltage=0.2V | -1.0   |     | 1.0     | mA   |

| SDL    | Differential nonlinearity           |                                                                          | -1.0   |     | 1.0     | LSB  |

| SL     | Nonlinearity                        | \/oo_E 12\//20m\//LSB\                                                   | -1.5   |     | 1.5     | LSB  |

| Szero  | Zero code error                     | Vcc=5.12V(20mV/LSB) without load (IAO=0)                                 | -2.0   |     | 2.0     | LSB  |

| SFULL  | Full scale error                    |                                                                          | -2.0   |     | 2.0     | LSB  |

| Со     | Output capacitative load            |                                                                          | _      | _   | 0.1     | μF   |

| Ro     | Buffer amplifier output inpedance   |                                                                          |        | 5.0 |         |      |

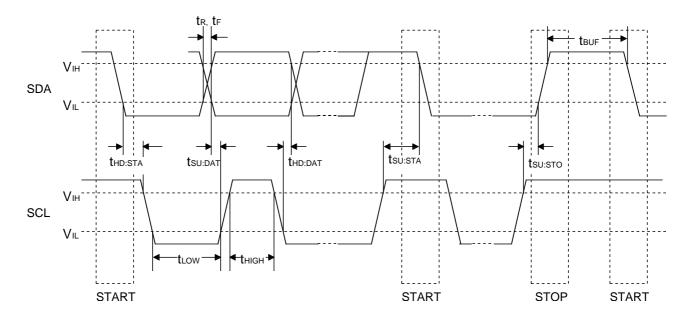

# I'C BUS LINE CHARACTERISTICS

| Symbol  | Parameter                                                                         | Min. | Max. | units |

|---------|-----------------------------------------------------------------------------------|------|------|-------|

| fscL    | SCL clock frequency                                                               | 0    | 100  | KHz   |

| tBUF    | Time the bus must be free before a new transmission can start                     | 4.7  | -    | μs    |

| thd:STA | Hold time START Condition. After this period, the first clock pulse is generated. | 4.0  | -    | μs    |

| tLow    | LOW period of the clock                                                           | 4.7  | -    | μs    |

| tHIGH   | HIGh period of the clock                                                          | 4.0  | -    | μs    |

| tsu:sta | Set-up time for START condition (Only relevant for a repeated START condition)    | 4.7  | -    | μs    |

| thd:dat | Hold time DATA                                                                    | 0    | -    | μs    |

| tsu:dat | Set-up time DATA                                                                  | 250  | -    | ns    |

| tR      | Rise time of both SDA and SCL lines                                               | -    | 1000 | ns    |

| tF      | Fall time of both SDA and SCL lines                                               | -    | 300  | ns    |

| tsu:sto | Set-up time for STOP condition                                                    | 4.0  | -    | μs    |

<sup>•</sup> Note that a transmitter must internally provide at least a hold time to bridge the undefined region (max.300 ns) of the falling edge of SCL.

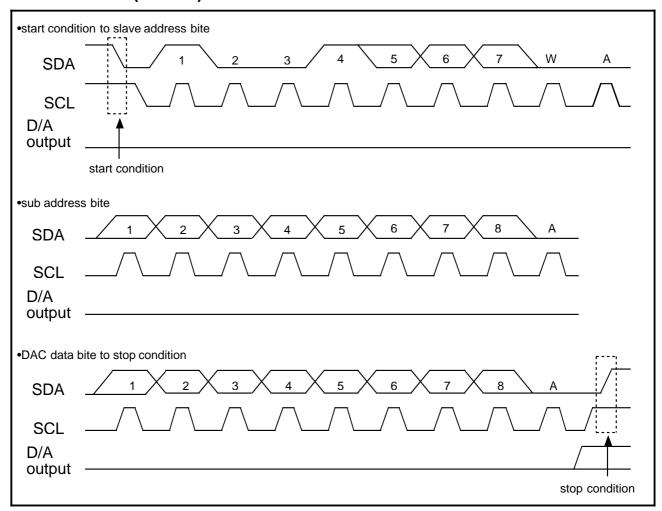

## **TIMING CHART**

### 8-BIT 3CH fC BUS D-A CONVERTER WITH BUFFER AMPLIFIERS

## I'C BUS FORMAT

| STA SLAVE ADDRESS W A | SUB ADDRESS A | DAC DATA | A STP |

|-----------------------|---------------|----------|-------|

|-----------------------|---------------|----------|-------|

STA: start condition W: write(SDA=Low)

A: affirmation bit STP: stop condition

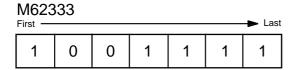

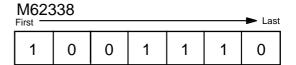

## • SLAVE ADDRESS

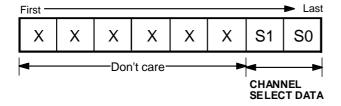

### • SUB ADDRESSS

### CHANNEL SELECT DATA

| S1 | S0 | Channel selection |

|----|----|-------------------|

| 0  | 0  | ch1 selection     |

| 0  | 1  | ch2 selection     |

| 1  | 0  | ch3 selection     |

| 1  | 1  | Don't care        |

## • DAC DATA

| First MSB |    |    |    |    |    |    |    |  |  |  |

|-----------|----|----|----|----|----|----|----|--|--|--|

| D7        | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

| First<br>MSB — |    |     |    |    |    |     | Last LSB |               |

|----------------|----|-----|----|----|----|-----|----------|---------------|

| D7             | D6 | D5  | D4 | D3 | D2 | D1  | D0       | DAC output    |

| 0              | 0  | 0   | 0  | 0  | 0  | 0   | 0        | Vcc/256 x 1   |

| 0              | 0  | 0   | 0  | 0  | 0  | 0   | 1        | Vcc/256 x 2   |

| 0              | 0  | 0   | 0  | 0  | 0  | 1   | 0        | Vcc/256 x 3   |

| 0              | 0  | 0   | 0  | 0  | 0  | 1   | 1        | Vcc/256 x 4   |

| :              | :  | • • | •• | •• | •• | • • | :        | :             |

| 1              | 1  | 1   | 1  | 1  | 1  | 1   | 0        | Vcc/256 x 255 |

| 1              | 1  | 1   | 1  | 1  | 1  | 1   | 1        | Vcc           |

# TIMING CHART (MODEL)

•Start condition With SCL at HIGH,SDA line goes from HIGH to LOW

•Stop condition With SCL at HIGH,SDA line goes from LOW to HIGH

(Under normal circumstances, SDA is changed when SCL is LOW)

•Acknowledge bit The receiving IC has to pull down SDA line whenever receive slave data.

(The transmitting IC releases the SDA line just then transmit 8bit data.)

## **Digital Data Formats**

| STA | SLAVE ADD | RE | SS     | W     | Α   | SUB AD | DRESS 1  | А    | DAC I | DATA 1 | А    |   |     |

|-----|-----------|----|--------|-------|-----|--------|----------|------|-------|--------|------|---|-----|

|     |           |    |        |       |     |        |          |      |       |        |      | _ |     |

| SUB | ADDRESS 2 | Α  | DAC DA | ATA 2 | 2 A | ]      | SUB ADDF | RESS | n A   | DAC DA | TA n | А | STP |

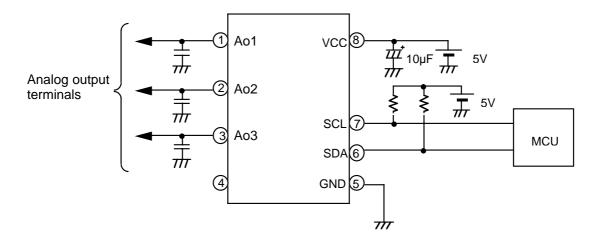

#### PRECAUTION FOR USE

Supply voltage terminal(Vcc) is also used for D-A converter upper reference voltage setting. IF ripple or spike is input this terminal, accuracy of D-A conversion is down. So, when use this device, please connect capacitor among Vcc to GND for stable D-A conversion.

This IC's output amplifier has an advantage to capacitive load. So it's no problem at device action when connect capacitor (0.1 $\mu$  F MAX) among output to GND for every noise eliminate.

#### **APPLICATION EXAMPLE**

#### -Note regarding I<sup>2</sup>C BUS-

• Purchase of MITSUBISHI ELECTRIC CORPORATION'S I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components an I<sup>2</sup>C system,provided that the system comforms to I<sup>2</sup>C Standard Specification as defined by Philips.

### Keep safety first in your circuit designs!

• Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury,fire or property damage. Remember to give due consideration to safety when making your circuit design, in order to prevent fires from spreading, redundancy, malfunction or other mishap.